Учебная дисциплина: схемотехника

Руководитель: Дудко А.В.

Выполнил: студент группы 17БСТ(бп)ИДМБ Драгун Кристина

Дешифраторы

Дешифраторы

- Дешифратором называется комбинационная схема с несколькими входами и выходами, преобразующая код, подаваемый на входы, в сигнал на одном из выходов (так называемый унарный код ).

- Если на входы дешифратора подаются двоичные переменные, то на одном из выходов дешифратора вырабатывается сигнал 1, а на остальных выходах сохраняются нули.

Дешифраторы

- Число входов и выходов в так называемом полном дешифраторе связано соотношением

- m=2 n , где n — число входов, а m — число выходов.

- Если в работе дешифратора используется неполное число выходов , то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

Дешифраторы

- На выходах дешифратора вырабатываются значения булевых функций соответственно:

- F0=!Xn * !Xn-1*…………* !X3 * !X2 *!X1 ;

- F1=!Xn * !Xn-1*………….* !X3 * !X2 * X1 ;

- F2=!Xn * !Xn-1*………….* !X3 * X2 * !X1 ;

- F3=!Xn * !Xn-1*………….* !X3 * X2 * X1 ;

- F4=!Xn * !Xn-1*………….* X3 * !X2 * !X1.

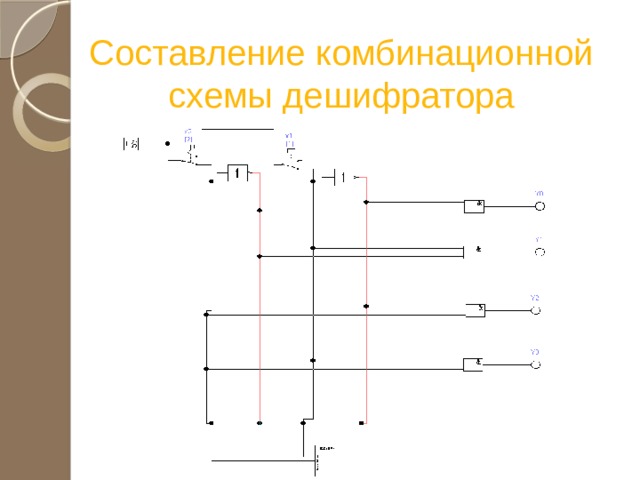

Составление комбинационной схемы дешифратора

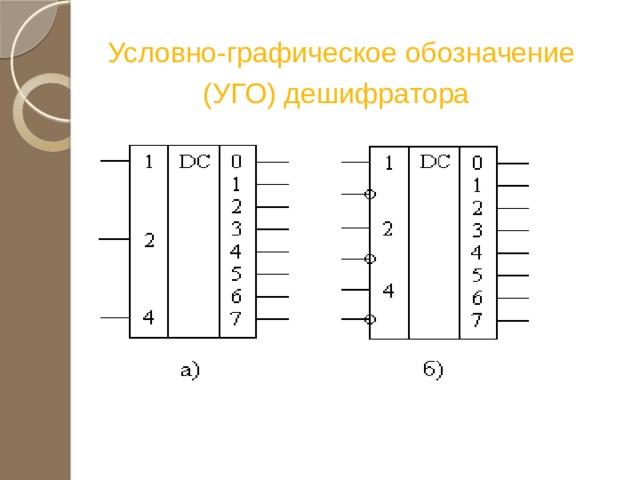

Условно-графическое обозначение (УГО) дешифратора

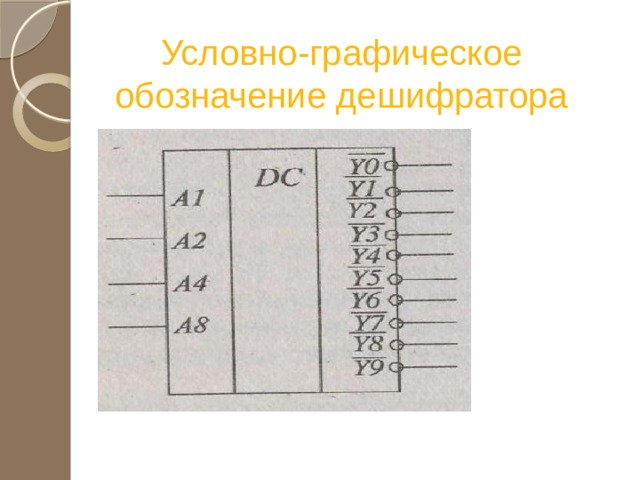

Условно-графическое обозначение дешифратора

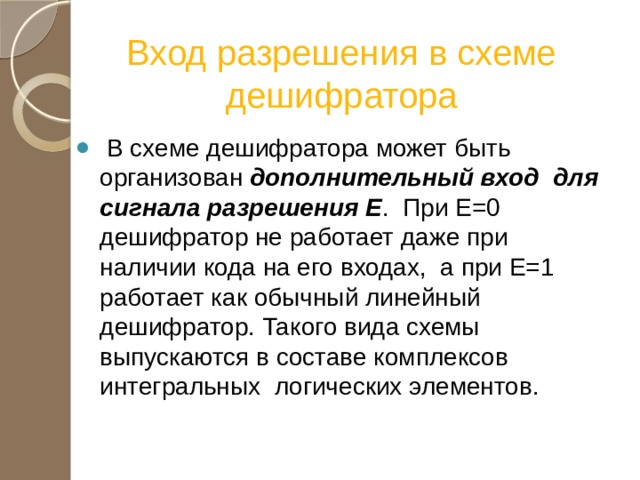

Вход разрешения в схеме дешифратора

- В схеме дешифратора может быть организован дополнительный вход для сигнала разрешения Е . При Е=0 дешифратор не работает даже при наличии кода на его входах, а при Е=1 работает как обычный линейный дешифратор. Такого вида схемы выпускаются в составе комплексов интегральных логических элементов.

Каскадное включение дешифраторов

- Из логических элементов, являющихся дешифраторами, можно строить дешифраторы на большее число входов , при этом, как правило, используются дешифраторы с дополнительными входами сигнала разрешения. Каскадное включение таких схем позволяет легко наращивать число дешифрируемых переменных.

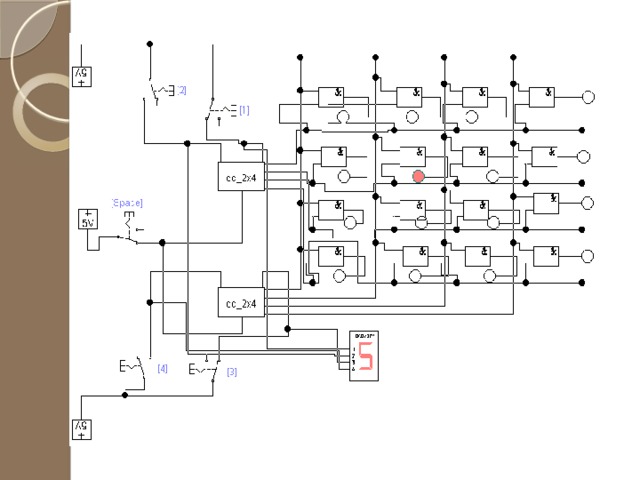

Матричная схема включения дешифраторов

- Другим способом реализации дешифратора на количество выходов, превышающее количество выходов в имеющихся микросхемах дешифраторов это составление матричной схемы построения составного дешифратора.

Матричная схема включения дешифраторов

- В матричной схеме используются два идентичных по размерности дешифратора, выходы одного образуют горизонтальные линии, выходы другого - вертикальные линии. Эти линии составляют матрицу, но не соединяются между собой.

Матричная схема включения дешифраторов

- В ячейках этой сетки матрицы устанавливаются логические элементы «И» или «И-НЕ», один из входов которых соединяется с горизонтальной линией (выход), другой с вертикальной линией. Выходы этих логических элементов и будут выходами построенного дешифратора большей размерности.

Получите свидетельство

Получите свидетельство Вход

Вход

Разработка симулятора пациента ЭКГ (139.17 KB)

Разработка симулятора пациента ЭКГ (139.17 KB)

0

0 93

93 1

1 Нравится

0

Нравится

0